-

价格:未填

-

起订:5

-

供应:10000

TI KeyStone TMS320C665x + Xilinx Artix-7 FPGA开发板简介

广州创龙结合TI KeyStone系列多核架构TMS320C665x及Xilinx Artix-7系列FPGA设计的SOM-TL665xF核心板是一款DSP+FPGA高速大数据采集处理平台,用沉金无铅工艺的12层板设计,适用于高端图像处理、高速大数据传输和音视频等大数据采集处理领域。

核心板在内部通过uPP、EMIF16、SRIO通信接口将DSP与FPGA结合在一起,组成DSP+FPGA架构,实现了需求独特、灵活、功能强大的DSP+FPGA高速数据采集处理系统。

SOM-TL665xF引出DSP及FPGA全部资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。创龙不仅提供丰富的Demo程序,还提供DSP核间通信、DSP与FPGA间通讯开发教程以及全面的技术支持,协助客户进行底板设计和调试以及多核软件开发。

Ø 基于TI KeyStoneC66x多核定点/浮点DSP MS320C665x + Xilinx Artix-7 FPGA处理器;

Ø TMS320C665x主频为1.0/1.25GHz,每核运算能力高达40GMACS和20GFLOPS,每核心32KByte L1P、32KByte L1D、1MByte L2,1MByte多核共享内存,8192个多用途硬件队列,支持DMA传输;

Ø FPGA芯片型号为XC7A100T-2FGG484I,逻辑单元101K个,DSP Slice 240个;

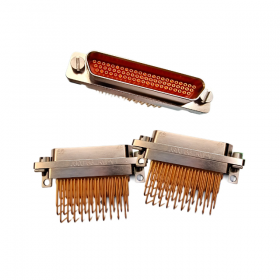

Ø TMS320C665x与FPGA内部通过uPP、EMIF16、SRIO连接,其中SRIO每通道传输速度最高可达到5GBaud;

Ø 支持PCIe、uPP、EMIF16、SRIO、千兆网口等多种高速接口,同时支持I2C、SPI、UART、McBSP等常见接口;

Ø 可通过DSP配置及烧写FPGA程序且DSP和FPGA可以独立开发,互不干扰;

Ø 连接稳定可靠,100mm*65mm,采用工业级精密B2B高速连接器,关键大数据接口使用高速连接器,保证信号完整性;

Ø 提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

高端图像处理

软件无线电

雷达声纳

高端数控系统

机器视觉

TI KeyStone TMS320C665x + Xilinx Artix-7 FPGA开发板硬件参数

表 SEQ 表 * ARABIC 1 DSP端硬件参数

CPU | 单核TMS320C6655/双核TMS320C6657,主频1.0/1.25GHz |

ROM | 128Mbit SPI NOR FLASH |

128MByte NAND FLASH | |

RAM | 512M/1GByte DDR3 |

EEPROM | 1Mbit;兼容ATAES132A-SHER加密芯片(可选) |

SENSOR | 1x TMP102AIDRLT,核心板温度传感器,I2C接口 |

B2B Connector | 4x 100pin高速B2B连接器,间距0.5mm,合高5.0mm,共400pin,信号速率可达10GBaud |

LED | 1x供电指示灯 |

2x用户指示灯 | |

硬件资源 | 1x SRIO,四端口四通道(两通道与GTP内部连接,两通道外部引出),每通道最高通信速率5GBaud |

1x PCIe Gen2,单端口双通道,每通道最高通信速率5GBaud | |

1x SGMII,10/100/1000M Ethernet | |

1x EMIF16,16bit | |

2x McBSP | |

2x UART | |

1x I2C | |

1x SPI | |

2x Timer | |

32x GPIO | |

1x JTAG | |

1x BOOTMODE,13bit |

表 SEQ 表 * ARABIC 2 FPGA端硬件参数

FPGA | Xilinx Artix-7 XC7A100T-2FGG484I |

ROM | 256Mbit SPI NOR FLASH |

RAM | 512M/1GByte DDR3 |

Logic Cells | 101440 |

DSP Slice | 240 |

LED | 1x PRO指示灯 |

3x用户指示灯 | |

硬件资源 | 4x GTP(2个GTP与SRIO内部连接,2个外部引出) |

1x UART | |

1x I2C | |

130x GPIO | |

1x JTAG |

软件参数

表 SEQ 表 * ARABIC 3

DSP端软件支持 | 裸机、SYS/BIOS操作系统 |

CCS版本号 | CCS5.5 |

软件开发套件提供 | MCSDK |

VIVADO版本号 | 2015.2 |

TI KeyStone TMS320C665x + Xilinx Artix-7 FPGA开发板开发资料

(1) 提供核心板引脚定义、可编辑底板原理图、可编辑底板PCB、芯片Datasheet,缩短硬件设计周期;

(2)提供丰富的Demo程序,包含DSP多核通信教程,完美解决多核开发瓶颈;

(3)提供DSP与FPGA通过SRIO、EMIF16、I2C等相关通讯例程;

(4) 提供完整的平台开发包、入门教程,节省软件整理时间,上手容易;

部分开发例程详见附录A,开发例程主要包括:

Ø 裸机开发例程

Ø SYS/BIOS开发例程

Ø 多核开发例程

Ø FPGA开发例程

-

公司:广州创龙电子科技有限公司

-

姓名:创龙(先生)

-

电话:13360029811

-

手机:13360029811

-

传真:020-89986280

-

地区:广东-广州市

-

邮编:510000

-

QQ:2310015505

-

0人关注0人点赞举报